# Introduction to the Motorola 68HC908JB8

Jean-Michel FRIEDT, December 2001-October 7, 2004

### 1 Introduction

We decided to look at the 68HC908JB8 microcontroller from Motorola following interest in the development of USB enabled intruments. The 68HC908JB8 does not require any external programmer since it is based on flash memory, provides a convenient communication tool in ROM called the Monitor mode, includes one USB peripheral but no UART. It is available both is easy to handle DIP package and low volume SOIC package.

All development were done under Linux (kernel 2.2.19, although no kernel specific functions were used) using gcc 2.95.2 for generating the binaries running on the PC and as6808 v.03.10 provided by asxxxx v.3.10 (November 2001) for the programs running on the microcontroller.

The following script was used for generating the ASCII file containing the hexadecimal codes of the program to be transferred from the PC to the microcontroller:

| <pre>#!/usr/bin/tcsh if ( \$# == 0 ) then</pre> | ./as6808 - | "->" \$nom".out" |

|-------------------------------------------------|------------|------------------|

|-------------------------------------------------|------------|------------------|

asm: script for compiling a text file containing the assembly program to an ASCII file containing the hexadecimal opcodes.

Once the .out ASCII file containing the hexadecimal opcodes is generated, the board is switched on and the program is uploaded using ./hc08 file.out where hc08 is a program described later developed for the purpose of learning how this microcontroller works. But first we must look at the hardware before being able to test our first program.

### 2 Electronic circuit

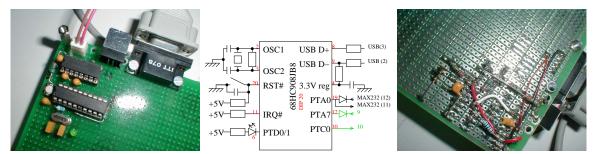

The electronic circuit around the 68HC908JB8 is quite simple and highly inspired from the development circuit provided by Motorola. It mainly consists of the oscillator circuit, pull up resistors to the interrupt (IRQ#) and PTA0 lines, and the reset switch. Since the PTA0 line, which is used for communication in the monitor mode with the PC through the MAX232, includes its own internal pull up resistor, adaptation between the TTL (5 V) logic of the MAX232 and the 3.3 V logic of the 68HC908JB8 is quite simple: a diode turned towards the highest voltage is enough. Indeed, if the MAX232 outputs a low level (pin grounded), the current can flow from the microcontroller to the MAX232 and PTA0 senses a ground level. If on the other hand the MAX232 pin is high (+5 V), the diode is blocking the current flow from the microcontroller to the MAX232 and the PTA0 pin senses a high (+3.3 V) level thanks to its pull up resistor.

Simple circuit for communicating with the 68HC908JB8 microcontroller. The green lines are optional connections between the microcontroller and the MAX232 in order to use a second software emulated UART. The red numbers are the pin numbers for a 20 pin DIP package.

### 3 The Monitor mode

First, we must find out how to program the 68HC908 and get familiar with its monitor feature. To this date (December 2001-January 2002) one program exists for programming two of the 68HC908 family: spgmr08, version 0.9. However, this software aims at integrating a lot of features in one bulky executable, including a GUI, which is not what I was looking for. And anyway, understanding every steps of the programming part of the microcontroller is interesting. So after building a basic board including a CPU, a MAX232 RS232 level converter and a few passive components as described earlier, I started putting together a few routines for getting familiar with the monitor mode.

Two tricks appeared:

- when sending the 8 security bytes at the beginning of the transmission, a delay between the received echo and the new

transmission is required

- the echo does not include one but two characters: the direct connexion through the protection diode of the RS232 transmission line with its reception line, followed by the echoed character by the microcontroller.

The monitor mode is otherwise implemented as described in section 10 of the Technical Data book. It allows reading and writing individual bytes or sequentially to any place in the microcontroller's memory, including to the I/O ports which makes testing simple circuits very easy. As a first example, let us make an LED connected to port D pin 0/1 (on the 20 pin DIP package) blink under computer control. We here write to the port D register from the PC: no program is running on the microcontroller itself (apart from the Monitor routine provided in ROM).

| /* All examples have been derived from miniterm.c */                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <pre>// newtio.c_cc[VSWTC] = 0; /* '\0' */</pre>                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| /* Don't forget to give the appropriate serial ports the right permissions $*/$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <pre>// newtio.c_cc[VSTART] = 0; /* Ctrl-q */</pre>                            |

| /* (e. g.: chmod a+rw /dev/ttyS0) */                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <pre>// newtio.c cc[VSTOP] = 0; /* Ctrl-s */</pre>                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <pre>// newtio.c_cc[VSUSP] = 0; /* Ctrl-z */</pre>                             |

| #include "rs232.h"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <pre>// newtio.c_cc[VEOL] = 0; /* '\0' */</pre>                                |

| "Include Include Inclu | <pre>// newtio.c cc[VREPRINT] = 0; /* Ctrl-r */</pre>                          |

| extern struct termios oldtio, newtio;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <pre>// newtio.c_cc[VDISCARD] = 0; /* Ctrl-u */</pre>                          |

| extern struct termios ofutio, newtro,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                |

| int init_rs232(int BAUDRATE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <pre>// newtio.c_cc[VLNEXT] = 0;  /* Ctrl-v */</pre>                           |

| {int fd;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | // newtio.c_cc[VEOL2] = 0; /* '\0' */                                          |

| fd=open(HC11DEVICE, 0_RDWR   0_NOCTTY );                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <pre>tcflush(fd, TCIFLUSH);tcsetattr(fd,TCSANOW,&amp;newtio);</pre>            |

| if (fd <0) {perror(HC11DEVICE); exit(-1); }                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <pre>// printf("RS232 Initialization done\n");</pre>                           |

| tcgetattr(fd,&oldtio); /* save current serial port settings */                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | return(fd);                                                                    |

| bzero(&newtio, sizeof(newtio)); /* clear struct for new port settings */                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3                                                                              |

| // newtio.c_cflag = BAUDRATE   CRTSCTS   CS8   CLOCAL   CREAD;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                |

| newtio.c_flag = BAUDRATE   CS8   CLOCAL   CREAD; /* _no_ CRTSCTS */                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | void sendcmd(int fd,char *buf)                                                 |

| newtio.c_iflag = IGNPAR; //   ICRNL   IXON;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | {unsigned int i, j;                                                            |

| newtio.c_oflag = IGNPAR; // ONOCR [ONLRET]OLCUC;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | if((write(fd,buf,strlen(buf))) <strlen(buf))< td=""></strlen(buf))<>           |

| // newtio.c_lflag = IGANON;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <pre>{printf("\n No connection\n");exit(-1);}</pre>                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                |

| <pre>// newtio.c_cc[VIINTR] = 0; /* Ctrl-c */</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | for (j=0;j<5;j++) for (i=0;i<3993768;i++) {}                                   |

| // newtio.c_cc[VQUIT] = 0; /* Ctrl-\ */                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | /* usleep(attente); */                                                         |

| // newtio.c_cc[VERASE] = 0; /* del */                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3                                                                              |

| // newtio.c_cc[VKILL] = 0; /* @ */                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                |

| <pre>// newtio.c_cc[VEOF] = 4; /* Ctrl-d */</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | void free_rs232(int fd)                                                        |

| <pre>newtio.c_cc[VTIME] = 0; /* inter-character timer unused */</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | {tcsetattr(fd,TCSANOW,&oldtio);close(fd);} /* restore the old port settings */ |

| <pre>newtio.c_cc[VMIN] = 1; /* blocking read until 1 character arrives */</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                |

rs232.c: basic RS232 initialization routine needed for all programs running under Linux requiring access to the serial port.

| <pre>#include <stdio.h> #include <stdlib.h> #include <unistd.h></unistd.h></stdlib.h></stdio.h></pre>                                                              |                                         | <pre>int init_rs232();<br/>void free_rs232();<br/>void sendcmd(int,char*);<br/>struct termios oldtio,newtio;</pre> |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| <pre>#include <sys types.h=""> #include <sys stat.h=""> #include <string.h> #include <fcntl.h> #include <fcrtl.h></fcrtl.h></fcntl.h></string.h></sys></sys></pre> | <pre>/* declaration of bzero() */</pre> | // #define BAUDRATE B9600<br>// #define BAUDRATE B19200<br>#define HC11DEVICE "/dev/ttyS0"                         |

rs232.h: header for the basic RS232 initialization routines.

```

// test hardware: make a diode blink from monitor (MON) mode

lo=0x03; hi=0; writ_hc08(fd,hi,lo,0x00);

sleep(1);

#include "hc08.h

3

void hc08_test(int fd)

{char lo,hi;

lo=0x56; hi=0; read_hc08(fd,hi,lo);

void hc08_prg(int fd)

Vold neco_prg.ne 14;

{char lo,hi;

lo=0x00; hi=0x01; writ_hc08(fd,hi,lo,0x00);

iwrit_hc08(fd,0x22);

lo=0x56; hi=0; read_hc08(fd,hi,lo);

lo=0x57; hi=0; read_hc08(fd,hi,lo);

lo=0x56; hi=0; read_hc08(fd,hi,lo);

lo=0x56; hi=0; read_hc08(fd,hi,lo);iread_hc08(fd);

lo=0x56; hi=0; writ_hc08(fd,hi,lo,0x50);

lo=0x56; hi=0; read_hc08(fd,hi,lo);iread_hc08(fd);

i=10; hc08(fd,0=20).

readsp_hc08(fd);

int main(int argc, char **argv)

iwrit_hc08(fd,0x32);

{int fd:

lo=0x59; hi=0; read_hc08(fd,hi,lo);

fd=init rs232(B9600):

10=0x09; n1=0; real_nc00(rd,n1,10);

readsp_hc08(fd);

lo=0x07; h1=0; writ_hc08(fd,h1,l0,0xFF);

while(1) {

fawint_rs23(b900);

init_hc08mon(fd);fre_rs232();

fd=init_rs232(B9600);// forget the 10 stop bits

hc08_test(fd);

lo=0x03; hi=0; writ_hc08(fd,hi,lo,0xFF);

free_rs232();

sleep(1);

```

Test programming for controlling the blinking of an LED connected to port D pin 0/1 (20 pin DIP package) controlled from a Linux running PC.

Once we have checked the basic circuitry around the microcontroller is operating properly, we can go on to the next step of performing the same task (blinking an LED) from a program stored on board the microcontroller. The slight additional difficulty is to figure out how to setup the memory in the microcontroller before sending a RUN command to the monitor. I found the answer in a comment to spgmr08, in mongp32.c (comment to the routine mon\_runpc()): after asking the monitor the current position of the stack pointer (SP), we simply store in SP+4 the high byte of our program's starting address and in SP+5 the lower byte of our program's starting address. Since I have decided to store my program in the beginning of RAM space which starts at 0x0040, (SP+4)=0x00 and (SP+5)=0x40 in my case. After reset, the monitor mode defines the stack pointer to be located at 0x00FF, and uses a few bytes so that just before executing the RUN command, SP always appears to be equal to 0x00FA (=250d).

#### 3.1 Storing and executing a program from RAM

#include "hc08.h"

j

int main(int argc,char \*\*argv)

{int fd;FILE \*f;

if (argc<2) {printf("%s filename\n",argv[0]);} else {

fd=init\_rs232(); init\_hc08mon(fd);free\_rs232();fd=init\_rs232();// forget the 10 stop bits

f=fopen(argv[1],"r");

hc08\_prg(f,fd);

fclose(f);

free\_rs232();

} return(0);

}</pre>

Store a program in RAM (address 0x0040) and execute it.

DEBUG("\n RUN executed \n");

| <pre>start: ldhx #0x0140 ; TXS : (SP)&lt;-(H:X)-1 =&gt; STACK=0x013f<br/>txs ; reset stack pointer<br/>; mov #0x01,CONFIG1 ; disable COP watchdog, CONFIG1=0x001f<br/>clra ; clear accumulator<br/>mov #0x0f,0x0007 ; DDRD: port D as output</pre> | delay: psha<br>pshx<br>clrx ; 256*0,9375ms=240ms<br>loopz: clra ; 9*256*2304 (0,9375ms @ 2,4576MHz)<br>loopa: nsa ; [3] |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| loop: eor #0x0f ; toggle diode                                                                                                                                                                                                                     | nsa ; [3]<br>dbnza loopa ; [3]                                                                                          |

| sta 0x0003 ; store accumulator on PortD                                                                                                                                                                                                            | dbnzx loopx ;                                                                                                           |

| bsr delay                                                                                                                                                                                                                                          | pulx                                                                                                                    |

| bra loop                                                                                                                                                                                                                                           | pula                                                                                                                    |

|                                                                                                                                                                                                                                                    | rts                                                                                                                     |

blink.asm: sample program for blinking a LED connected to PTD0/1.

The limitation of this programming method is quickly obvious: since the default location of the stack pointer (SP) is 0x00FF, the RAM is cut in two halves (0x0040 to 0x00FA approximately, and 0x00FF to 0x013F) which only allows uploading to the microcontroller programs 186 and 64 bytes long respectively (depending whether we store the program below or above the stack pointer). Since our aim is USB development and the sample (short) program from Motorola already needs 1.8 KB, being able to store the code to flash memory and execute it from there seems mandatory. Our next steps will thus be to develop a software UART (since the 68HC908JB8 does not include an hardware UART) so we can receive new data from our own programs, and then to learn how to store data (the new program we want to save) in flash memory. This way, we will be able to test programs up to 8 KB long, which should be enough to get us started with USB development.

## 4 Asynchronous communication (software emulation)

First, we wish to transmit characters from the microcontroller to the PC.

| start: ldhx #0x0140 ; TXS : (SP)<-(H:X)-1 => STACK=0x013f  | bcc bit0 ; 3 branch if carry is clear (is A&1=0)      |

|------------------------------------------------------------|-------------------------------------------------------|

| txs ; reset stack pointer                                  | mov #0x01,0x0000 ; 4 PTA0=hi                          |

| ; mov #0x01,CONFIG1 ; disable COP watchdog, CONFIG1=0x001f | bra bit1 ; 3                                          |

| -                                                          | bit0: mov #0x00,0x0000 ; 4 PTA0=10                    |

| mov #0x00,0x0003 ; PTD0/1 lo => LED lit                    | bit1: dbnzx looprs ; 3> sum=11 or 14                  |

| mov #0x03,0x0007 ; DDRD: PTD0/1 as output                  | fin: bsr delay                                        |

|                                                            | bsr delay                                             |

| mov #0x01,0x0000 ; PTA: PTAO hi                            | mov #0x01,0x0000 ; PTA: PTA0 hi : STOP bit            |

| mov #0x01,0x0004 ; DDRA: PTAO as output                    | bsr delay                                             |

| ldx #0h00                                                  | bsr delay                                             |

| loop: incx ; increment counter                             | pulx                                                  |

| txa                                                        | rts                                                   |

| bsr send; send value of counter to serial port             |                                                       |

| bra loop                                                   | delay: pshx ; 2+4 for bsr (12+2*((X*9)+15))*.3333=833 |

|                                                            | ldx #0h0f ; 3 104                                     |

| send: pshx                                                 | loopx: nsa ; 3 => Xinit=0x88 for 1200                 |

| ldx #0x08 ; snd through PTA0 the content of Acc (@9600)    | nsa ; 3 =0x0f for 9600                                |

| mov #0x00,0x0000 ; PTA: PTA0 lo : START bit                | dbnzx loopx ; 3                                       |

| looprs: bsr delay ; X                                      | pulx ; 2                                              |

| bsr delay ; X                                              | rts ; 4                                               |

| rora : 1 rotate right Acc through carry                    |                                                       |

rs\_snd.asm: sample program for sending the values of a free running counter to the serial port. The baud rate is defined by the delay value in the function delay (0x88 for 1200 baud, 0x0f for 9600 baud communication).

| #include "rs232.h"                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>void read_osc(int fd) {ussigned char buf; while (1) {read(fd,&amp;buf,1); printf ("%u(\$%x) \n",buf&amp;Ox000000FF,buf&amp;Ox00000FF); fflush(stdout);}</pre> |

|                                                                                                                                                                    |

void main(int argc,char \*\*argv)

{int fd;

fd=init\_rs232();

read\_osc(fd);

free\_rs232();

}

hc08rec.c: sample program for reading the values on the RS232 port and displaying their decimal and hexadecimal values.

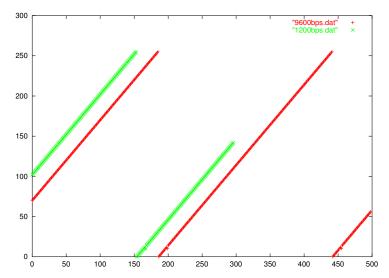

Result of transmitting the values of a free running counter (increasing) at 1200 (green) and 9600 (red) bauds. All data were correctly transmitted from the microcontroller running the software UART to the PC.

Now that we understand how to transmit arbitrary values from the microcontroller to the PC, we also want the microcontroller to be able to read values from the serial port and process them (for example add 3 and send the result back).

| start: ldhx #0x0140 ; TXS : (SP)<-(H:X)-1 => STACK=0x013f    | fin: bsr delay                                                                 |

|--------------------------------------------------------------|--------------------------------------------------------------------------------|

| txs ; reset stack pointer                                    | bsr delay                                                                      |

| ; mov #0x01,CONFIG1 ; disable COP watchdog, CONFIG1=0x001f   | mov #0x01,0x0000 ; PTA: PTA0 hi : STOP bit                                     |

| -                                                            | bsr delay                                                                      |

| mov #0x00,0x0003 ; PTD0/1 lo => LED lit                      | bsr delay                                                                      |